1. 비메모리 시장 전망

줄어드는 공급자 수, 늘어나는 수요

- 수요: 5G 스마트폰 반도체 채용 + 데이터센터 HPC(High Performance Computing)용 반도체 수요 지속 증가

- 공급: 선단공정 공급 과점화

→ 파운드리 단가 상승

미세화가 될수록 난이도는 어렵고 진입장벽은 커진다.

프로세서의 다양화

- 기존 CPU 중심에서 GPU, FPGA, ASIC으로 다양해짐

- 데이터센터 업체들이 AI 서비스 구현을 위한 칩 자체 설계해 사용하는 경우도 증가

- 애플은 인텔 CPU 버리고 ARM 기반의 자체 CPU로의 전환 선언

- ‘21년 출시될 CPU부터 단계적으로 자사 설계 CPU로 교체할 계획

인텔이 외주 생산 전환 시 파운드리 슈퍼 사이클은 더욱 앞당겨질 것

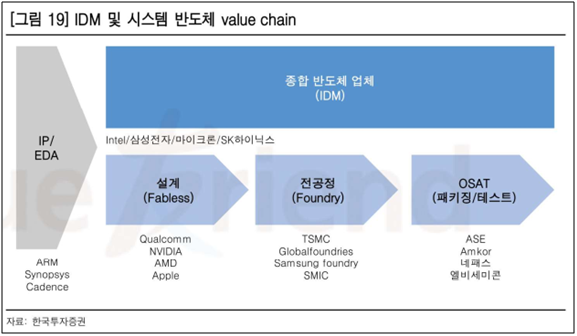

2. 비메모리 밸류 체인

- IP 반도체 칩 디자인할 때 사용되는 설계 블록

- EDA 다양한 IP를 활용해 전체 칩 설계를 할 수 있는 소프트웨어 툴

IP를 조합해 mask 위에 회로 설계를 함 → 포토 마스크

개발한 IP는 팹리스, 파운드리 혹은 디자인하우스에 판매

IP 판매 시 사용료 받고 양산시 wafer 매출액에 따라 로열티도 지급 받는 구조

- 디자인하우스

팹리스 고객사가 많아지면 파운드리 혼자서는 다 못함

팹리스 설계 요청이 오면 필요한 IP를 구매, 마스크 설계

향후 칩이 양산되면 후공정까지 턴키로 서비스

설계 과제 매출과 양산 매출 발생

시스코, 구글, SKT 등 통신 업체들은 AI 반도체를 개발하고 있는데 mask를 만들어본 경험이 없음

이러한 고객들에게 파운드리 역할을 대신하는 게 디자인 하우스 역할

디자인하우스의 경쟁력은 인력과 IP 보유 여부

개발자가 설계할 수 있는 레퍼런스 여부가 팹리스 고객사 수주 결정 변수

디자인하우스 자체 IP 보유했을 경우 마진을 많이 남길 수 있음

대만 디자인하우스와 달리 우리나라 디자인하우스는 인력 및 IP 경쟁력 떨어짐

꾸준한 M&A 통해 인력 보강하고 있음

→ 자본력이 중요

- 파운드리

미세화가 심화, 공정 난이도가 어려워 지면서 원래 설계한대로 제조 결과물이 나오지 않는 경우가 생김

설계와 결과물이 일치하려면 검증된 IP 최대한 많이 확보하는 것이 관건

파운드리 입장에서는 마스크 설계를 돕기 위한 IP/EDA, 디자인하우스 등 협력 관계와 생태계 구축 필연적

3. 파운드리 업체의 경쟁력

파운드리 업체들에게 요구되는 핵심 역량은?

1) 납기 대응력 2) 전공정 기술 3) 후공정 기술

1) 납기 대응력

IP를 많이 보유한 파운드리 업체가 팹리스 업체의 납기를 빠르게 맞출 수 있음

TSMC가 IP 보유 절대적으로 앞서 있음

2) 전공정 미세화 전쟁

인텔은 팹라이트로

인텔은 지난 7월 7나노 공정 개발 지연과 외부 파운드리 사용 가능성 공식화

‘21년으로 예정됐던 인텔 7나노는 최소 2022~2023년으로 지연

과거 역사를 보면

14나노에서 트랜지스터 집적도는 인텔 >> TSMC > 삼성

인텔이 14나노에서 4년간 머무르는 동안 TSMC와 삼성은 10나노로 공정기술 격차 줄임

TSMC와 삼성 10나노 집적도는 인텔 14나노를 앞섬

삼성 7나노에서 EUV 먼저 도입했으나 TSMC 대비 공정 기술 앞서는 데 실패

삼성은 7나노에서 성능 개선과 EUV 적용 동시 추진했으나 EUV 수율 낮아지고 원가 높아지는 결과

EUV 수율 잡기 어려웠고 DUV 대비 공정 속도가 늦었음

TSMC 7나노 공정 전환에서 큰 폭의 성능 개선 이뤘고, 두번째 7나노 EUV 공정에서 수율 안정화

현재는

5나노 TSMC가 삼성전자 대비 양산시점 5개월 빨랐으며 삼성전자 대비 큰 폭의 성능 개선 이룸

TSMC가 집적도 높고, EUV 레이어수도 많음 -> 성능, 공정 효율 다 앞선다는 얘기

핵심은 EUV

전공정 미세화의 핵심은 EUV

인텔이 7나노 진입 못하는 것도 EUV가 큰 요인

2021년 이후 EUV 수요 폭발적으로 증가할 것

TSMC, 삼성 45~50K 당 10대 수준, 현재 양사 연간 100K 이상 투자 전망

인텔 역시도 2021년부터는 EUV를 도입한다는 계획이 존재

‘21년 ASML capa는 연간 30->40대 수준으로 늘어날 것

하이닉스와 인텔 R&D 수요 더해질 경우 ASML capa 초과

EUV supply chain으로는 포토레지스트, 블랭크 마스크, 펠리클이 있음

그 외

노광 공정 외에도 High-end 장비 소재에 대한 수요 급격히 증가

ALD(Atomic Layer Deposition)나 ALE(Atomic Layer Etching) 장비 필수

게이트 길이가 10나노 돌파하면서 원자 크기에 가까운 사이즈의 분자를 다뤄야 함

식각 소재는 물론, 증착에 이용되는 프리커서(High-K, Low-K 등)에 대한 연구도 진행

미세화를 위한 미래 로드맵

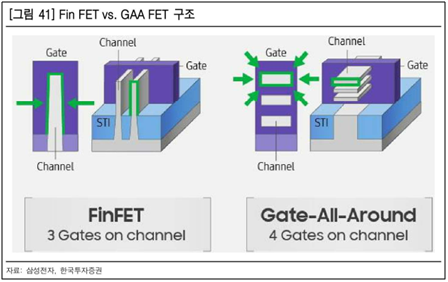

한편, 7나노 Fin FET 공정 이후 TSMC에게 선두를 빼앗긴 삼성은 3나노부터 GAA FET 시도할 계획

- 트랜지스터가 미세화될수록 소스와 드레인 사이의 위치가 가까워져 채널 길이가 짧아짐

- 전류를 통제하는 게이트의 능력(스위치 역할)이 저하

- 트랜지스터가 미세화될수록 누설 전류가 많아져 트랜지스터 성능 저하

누설전류를 해결하기 위해

28나노부터 HKMG(high k metal gate) 적용

유전율이 높은 금속 물질로 게이트와 채널 사이의 절연층 구성하여 채널 통제 능력 향상

14나노부터는 게이트와 채널의 접촉 면적을 넓혀 채널에 대한 통제를 강화하는 FinFet 도입

3나노부터는 접촉 면적을 3면 -> 4면으로 늘린 GAA Fet 적용하여 누설전류 문제 극복한다는 개념

삼성전자

3나노 GAA 공정에서 1세대를 GAE, 2세대를 GAP라 지칭

GAP 첫번째 후보군 MBCFET

GAE 이후 구조는 MBCFET 외에도 유망 반도체 소자 후보군 존재

- 나노와이어 → 나노시트 적층으로 유효 채널 너비 확대 가능할 뿐 아니라

- FinFET 공정과의 호환성도 높아 기존 설비와 제조 기술 활용 가능

TSMC

3나노까지 FinFET, 2나노부터 GAA로 전환

TSMC의 2나노 GAA는 삼성 3나노 GAP와 실질 성능이 유사할 것으로 전망

인텔

FinFET을 계속 유지하되 SuperFin이라는 구조 도입. 10나노 SuperFin

1) 트랜지스터 소재 자체의 저항을 낮추고 (구리 → 코발트)

2) 패널에 더 많은 전류가 빠르게 흐르도록 했으며,

3) 게이트를 통과하는 핀도 게이트와 5개의 면으로 맞닿도록 설계하여 전류 흐름을 보다 정밀하게 통제

-> 기존 10나노 대비 약 17.5%의 성능개선이 있다고 밝힘

3) 파운드리 후공정

후공정이 중요해지는 이유?

1) 기능은 모아야 하고 칩 크기는 작아져야 하고

2) 미세화를 통한 공정 개선은 힘들고 효율은 떨어지고

보통 몇 나노 공정이라고 하는 것은 소스 드레인 사이의 게이트 길이를 의미함

업체에서는 게이트 길이 7나노라 주장하지만 실제는 10나노 정도

게이트 길이가 제조업체의 마케팅적 요소가 되어 버렸음

이 얘기는 미세 공정 진행될수록 실질적 축소가 힘들어졌다는 것

실제로 전공정 미세화로 인한 성능 개선 폭은 점점 줄어들고 있음

그러나 후공정 변화에 따른 성능 개선폭은 매우 큼

후공정이 주목 받기 시작한 때는

’16년 TSMC의 애플 AP 단독 수주

TSMC fan-out 기술 양산에 성공한 ‘15년부터 TSMC 파운드리를 통해서만 제조

Fan Out 이란

반도체의 고성능화로 인해 입출력 단자 수 증가

칩 외부면적을 활용해 I/O단자를 배치

→ 디자인 유연성 제공, 반도체 성능 높여줌

→ 멀티 다이, System in Packaging에 유리한 방식

패키징 기술의 향후 발전 방향

선단공정에서 제조하는 칩일수록 OSAT에 외주를 주기보다는 파운드리가 제조에서 패키징까지 턴키로 서비스

향후 OSAT 업체보다는 대규모 설비투자를 할 수 있는 IDM/파운드리 위주의 패키징 기술 개발

패키징 기술은 SiP를 위한 3d 적층과 이기종 통합 패키징 방향으로 발전

- 모바일은 경박단소를 위해 fan-out 방식의 패키징 방식을 더 많이 활용

- HPC 애플리케이션은 chiplet 구조 활용

1) die마다 다른 공정 적용해 수율 높일 수 있고

2) 3d 패키징으로 칩 간 거리 줄여 전기 신호 이동속도 높이고 대역폭 늘림

차세대 패키징은 결국 적층 기술

미세화 발전 없이도 1) 면적당 집적도 향상, 2) 트랜지스터 간 배선 길이 축소,

3) 새로운 특성 창출

TSV(Through Silicon Via)

TSV는 칩 내부에 마이크로 홀 뚫어 칩 간 통신

와이어 불필요하므로 공간 활용도 상승

와이어로 인한 지연시간, 전력소모 해결

IP 설계 시 마이크로 홀 피해가야 하므로 설계 복잡성 증가

SoC의 경우 공간이 충분하지 못해 원칩화 어려움

기본적으로 발열 문제 심한 SoC 적층시 발열 문제 배로 증가

TSV의 기술적 한계로 TSV는 메모리에 우선 적용

2.5D의 등장

SoC는 TSV가 힘드니 DRAM은 TSV로 3D 적층하고, SoC는 Interposer를 통해 수평으로 배치

TSV가 궁극적인 패키징 기술이긴 하지만…

TSV의 높은 제조 기술 난이도와 비용

마이크로 홀 형성하고 구리를 박는 비용이 상당함

관통 전극 주변에는 저항을 막기 위해 데드 스페이스 발생 -> 다이 면적 증가

TSV를 적용해 제조한 HBM은 일반 칩 대비 높은 비용과 낮은 수율(일반 제품 대비 2배 이상 비쌈)

각 사의 패키징 로드맵

TSMC

Info (Integrated fan-out): TSMC의 이기종 통합 패키징용 fan-out 기술

CoWoS(Chip on Wafer on Substrate) : 인터포저 위에 여러 칩을 통합하는 2.5D 패키징 기술

차세대 패키징 기술인 SoIC 발표

상용화되진 않았으나 범프 간격을 10um 미만으로 줄일 수 있어 더 얇은 패키징 가능

인텔

한발 늦었지만 monolithic → chiplet으로

EMIB: 실리콘 인터포저 대신 실리콘 브릿지 사용하여 2D 연결

성능은 동일하나 실리콘 면적 감소해 원가 낮춤

Forveros: TSV 기술로 3D 적층

2021년 GPU 중 일부 TSMC 6나노 사용 예정. 외부 파운드리 쓰더라도 패키징은 자체적으로 가능하다는 것

삼성전자

모바일 패키징은 TSMC 대비 열위, HPC 패키징은 인텔 대비 열위

삼성이 TSMC 대비 상대적으로 가장 뒤쳐지는 부분은 패키징 → 적극 투자할 것으로 보임

차세대 기술 개발 크게 TSV, 적층 패키징(X-cube), FoPLP 세 방향

PLP(Panel Level Packaging)란

그럼 WLP(Wafer Level Packaging)란

웨이퍼 가공 후 하나씩 칩을 잘라내 패키징하던 기존 방식과 달리

웨이퍼 상태에서 한번에 패키지 공정 및 테스트를 진행한 후 칩을 절단하여 간단히 완제품을 만들어 내는 기술

RDL (Redistribution Layer) 공정을 통해 패키징 업체에서 직접 기판을 제작

WLP 방식은 기판(substrate)을 사용하지 않음

그 외

TSV 상용화 시 Chip-to-chip 연결 위해 드릴링 필요

정밀한 레이저 드릴링 각광

레이저 마킹, 커팅 하고 있는 기업이 어닐링 또는 드릴링 장비 시장에 진입하는 케이스 주목

Back grinding 관련 업체에 대한 관심도 필요

칩을 최대한 얇게 가공해야 하므로

연삭(Grinding) 및 연마(Polishing) 담당하는 기업뿐 아니라 라미네이션 공정 소재 등에도 관심 필요

→ 3가지 면에서 파운드리 업체를 비교해보았으며

TSMC가 현재까지는 압도적인 것으로 판단됨

그러나

삼성 파운드리 3분기부터 엔비디아 GPU 신모델인 Geforce RTX 30 시리즈 제품 양산 시작

파운드리 제품군이 모바일 AP 중심에서 IBM 서버용 CPU, 엔비디아 GPU로 확장

‘21년 퀄컴 high-end 모바일 AP, mid-end 모바일 AP, 엑시노스 1000, 퀄컴 5G 모뎀칩 등 생산 전망

삼성전자도 점차 레퍼런스를 쌓고 있고 미세화가 진행될수록 TSMC와의 격차는 줄어들 것임

4. 비메모리 OSAT

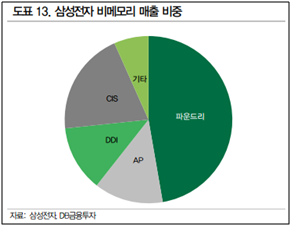

삼성전자 파운드리 외에도 비메모리 AP, CIS, DDI, PMIC 등을 설계하고 판매하는 매출 비중이 절반

이들의 후공정 일부는 삼성전자가 내재화하지만 대부분은 OSAT에서 외주 패키징과 테스트를 진행함

전방 애플리케이션은 삼성 스마트폰

스마트폰 고성능화, 화웨이 규제에 따른 수혜가 예상됨

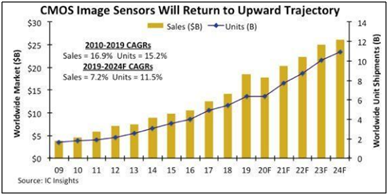

CIS는 Q의 측면에서 좋다.

- 스마트폰 카메라 대수가 점점 증가하고 있음

4~5개가 max겠지만 중저가폰까지 확산된다면 앞으로도 룸이 많이 남았을 것으로 봄

- 자율주행차 도입에 따른 수요 급증

이러한 이유로 소니와 삼성이 경쟁적으로 capa를 증가시키고 있음

CIS의 경우 테스나가 외주 테스트를 진행하고 있음

엘비세미콘이 CIS 테스트 사업 준비 중

DDI의 경우 P의 수혜를 받음

스마트폰 디스플레이가 LCD → OLED로 전환 중

이번 아이폰 모델 전부 OLED 적용

삼성의 DDI 범핑 공정은 스테코와 네패스가 진행하고 있었으나

OLED 모델 판매 증가 수요로 ‘18년부터 엘비세미콘이 벤더로 추가됨

PMIC는 Q의 수혜를 받음

5G 스마트폰 도입과 고성능화에 따라 배터리 용량도 증가하며

모듈 별로 전력을 저장하기 위해 PMIC가 더 많이 필요해짐

삼성전자 PMIC 패키징 및 테스트 물량의 대부분을 네패스가 담당하고 있었으나

2019년 하반기부터 엘비세미콘이 진입

SoC의 경우

삼성전자 RF 통신칩의 대부분을 테스나가 테스트 중

AP 테스트는 물량이 감소하여 삼성전자가 내재화

최근 삼성전자가 AP 물량에 대해 외주 테스트 추진하고 있으며 테스나와 엘비세미콘 등이 준비 중

향후 엘비세미콘이 좋아질 부분이 많다.

5. 생각

파운드리가 좋아지는 부분

인텔의 팹라이트화,

ARM 아키텍쳐 진영의 HPC 진출,

데이터센터 업체 등 AI 반도체 팹리스의 출현,

5G, 전장용 반도체, AR/VR와 같은 새로운 시스템 반도체 수요

TSMC와 삼성전자가 파운드리 시장을 양분하고 과실을 따먹을 것이다.

디자인하우스

여기가 다 차면 먹다 남은 게

디자인하우스로 올텐데 어떤 기업이 가장 수혜 받을지는 모르겠다.

여긴 엔터나 컨텐츠 업체와 같이 인력 싸움으로 본다.

좋은 인력을 영입하려면 자본 or 좋은 현금흐름이 있어야겠지?

파운드리는 현재 풀가동 중이라고 하는데 확인이 필요해 보이고

에이디테크놀러지에 7nm 경험한 인력들이 있다고 들어서 좋아 보인다.

코아시아도 기술적인 역량과 레퍼런스가 있는 것으로 아는데 재무적으로는 좋지 않다.

코아시아는 중저가 스마트폰 부품에서 주로 이익을 내고 있어서

현재 스마트폰 업황이 바닥을 탈출하고 있는 지금이 저렴하게 살 때가 아닌가 싶기도 한데

디자인하우스는 시장의 관심에서 멀어져 있다.

그럴수록 관심이 필요하다.

전공정 단에서는 EUV,

후공정 단에서는 패키징 그 중에서도 3D 적층과 SiP가 화두

EUV는 국내에서 수혜 받을 수 있는 기업은 한정적인데다가 이미 시장에 다 알려져서 밸류가 싸지 않다.

모르는 회사가 또 있을 수도

EUV로 전공정 스텝수가 감소하면서 의외로 증착, 식각 쪽은 재미가 없을 수도 있겠다는 생각이 든다.

후공정은 정말 확연하게도 SiP

고성능과 경박단소라는 어울리지 않는 두 목표를 달성해야 하는데 I/O가 문제다.

폰노이만 구조에서도 항상 발목을 잡는 건 I/O

I/O 문제를 해결하려면 고속도로를 만들고 길을 넓혀야 하는데 아예 다같이 한 집에서 살면 문제가 없다.

근데 어드밴스드 패키징으로 가는 길은 자금이 너무나 많이 필요해서 파운드리 업체가 다 해야할 것 같다.

SiP로 가는 큰 흐름에서 OSAT 업체가 수혜를 받기는 힘들어 보인다.

네패스가 fanout 패키징 기술을 갖고 있어서 그 측면에서는 좋아 보인다.

그렇지만 네패스는 투자의 시계열이 길어질 가능성이 높아서…

궁극적으로 패키징의 최고봉은 TSV인데 여기서 수혜를 받을 기업을 잘 찾아봐야 한다.

TSV는 DRAM에 먼저 본격적으로 적용될 텐데 적용되는 시점은 언제일까?

인텔 앨더레이크가 나오는 내년 말부터 DDR5가 도입되기 시작할 것이고

DDR5로의 전환과 함께 크기 증가로 인한 집적화도 해야 하니 TSV가 주목받지 않을까 싶은데

홀을 뚫기 위한 드릴링 기술,

비아를 형성하기 위한 어닐링 기술,

웨이퍼를 얇게 만들기 위한 그라인딩 기술을 가진 업체들을 공부해야 할 것 같다.

TSV에 대한 이해도가 떨어지는데 이런 자료들 보면서 공부해보자.

https://www.cheric.org/PDF/HHKH/HK54/HK54-6-0723.pdf

비메모리 OSAT 업체들은 스마트폰 변화에 따라 당연히 수혜를 받을 것인데

좋아지는게 확실하니 다들 OSAT 업체들를 주목하고 있기도 해서 그다지 땡기지가 않는다.

게다가 현 시점에서 가장 좋아보이는 엘비세미콘의 주가는 이미 달리고 있는 중이다.

결론은 디자인하우스와 TSV 수혜 업체 공부해보자.

'미국증시 시황' 카테고리의 다른 글

| 한국 반도체 장비 관련주 (0) | 2020.10.11 |

|---|---|

| 한국 반도체 소재,부품 관련주 (0) | 2020.10.11 |

| 주식 장기투자 쉽게 하는 법 (0) | 2020.10.09 |

| 실시간 주식 정보 알림 어플 D.ALARM(딸람) (0) | 2020.10.06 |

| 오사카거래소 키움증권도 가능(feat. 해외선물계좌) (0) | 2020.10.06 |